# Section 43. Graphics Controller Module (GFX)

## HIGHLIGHTS

This section of the manual contains the following topics:

| 43 | 3.1  | Introduction                      |  |

|----|------|-----------------------------------|--|

| 43 | 3.2  | Module Registers                  |  |

| 43 | 3.3  | Operation                         |  |

| 43 | 3.4  | Display Controller                |  |

| 43 | 3.5  | Graphical Processing Units (GPUs) |  |

| 43 | 3.6  | Interrupts                        |  |

| 43 | 3.7  | Display Power Sequencing          |  |

| 43 | 3.8  | Operation in Power-Saving Modes   |  |

| 43 | 3.9  | Effects of a Reset                |  |

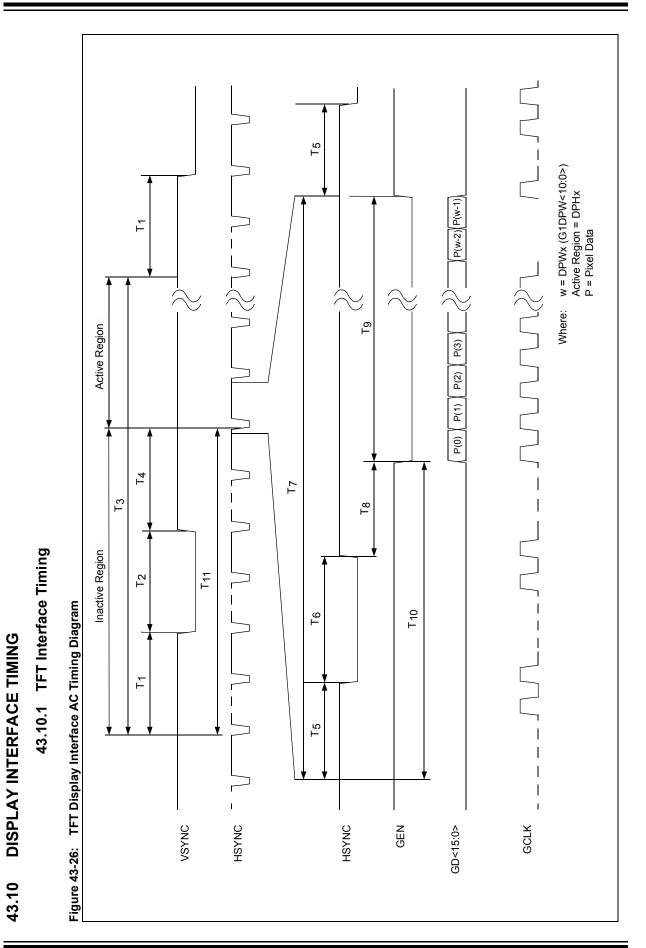

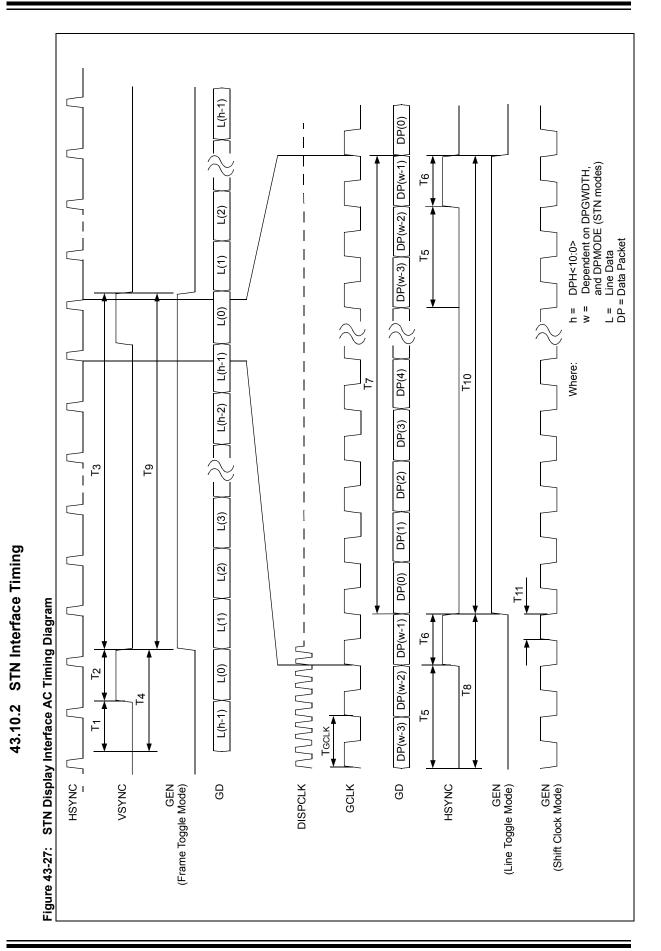

| 43 | 3.10 | Display Interface Timing          |  |

| 43 | 3.11 | Register Map                      |  |

| 43 | 3.12 | Related Application Notes         |  |

| 43 | 3.13 | Revision History                  |  |

43

### 43.1 INTRODUCTION

The Graphics Controller (GFX) module is specifically designed to directly interface with display glasses, with built-in analog drive, to individually control pixels in the screen. The module also provides accelerated rendering of vertical and horizontal lines, rectangles, copying of a rectangular area between different locations on the screen, drawing texts and decompressing compressed data. The use of the accelerated rendering is performed using command FIFO. Once initiated, the hardware will perform the rendering freeing up the CPU for other tasks. Software can either poll the status or use interrupts to continue rendering succeeding shapes.

### 43.1.1 GFX Module Features

The GFX module supports three categories of display glasses:

- Monochrome STN

- Color STN

- Color TFT

Programmable vertical and horizontal synchronization signals' timing is provided to meet the display's timing requirements.

The GFX module includes the following features:

- Graphics Hardware Accelerators:

- Character Graphics Processing Unit (CHRGPU)

- Rectangle Copy Graphics Processing Unit (RCCGPU)

- Inflate Processing Unit (IPU)

- 256 Color Look-up Table (CLUT) Entries

- Supports 1/2/4/8/16 bits-per-pixel (bpp) Color Depth

- Programmable Display Resolution

- Supports the following Display Interfaces:

- 4/8/16-Bit Monochrome STN

- 4/8/16-Bit Color STN

- 9/12/18/24-Bit Color TFT (18 and 24-bit displays are connected as 16-bit 5-6-5 RGB color format)

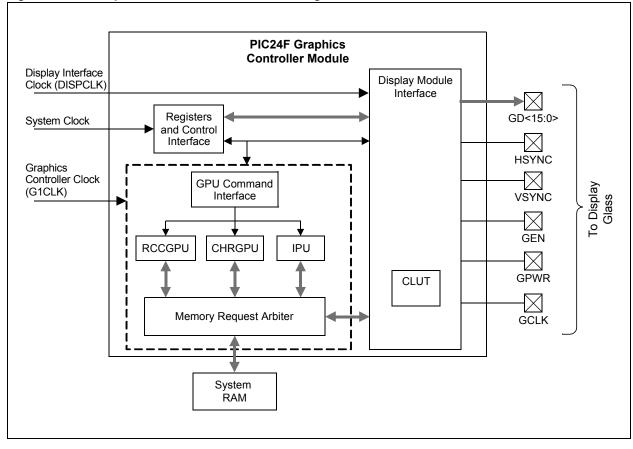

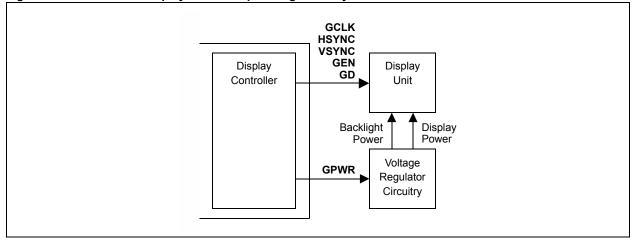

Figure 43-1 illustrates the GFX module pinout and image buffer sources. In some devices, system RAM can also reside externally to the device. Refer to the applicable device data sheet for details.

Figure 43-1: Graphics Module Pinout and Block Diagram

### 43.2 MODULE REGISTERS

The GFX module includes the following control and status registers:

• G1CMDL and G1CMDH – GPU Command Low/High Register (Register 43-1 and Register 43-2)

These registers form the 32-bit command field. Commands written to these registers are loaded to the command FIFO.

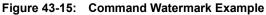

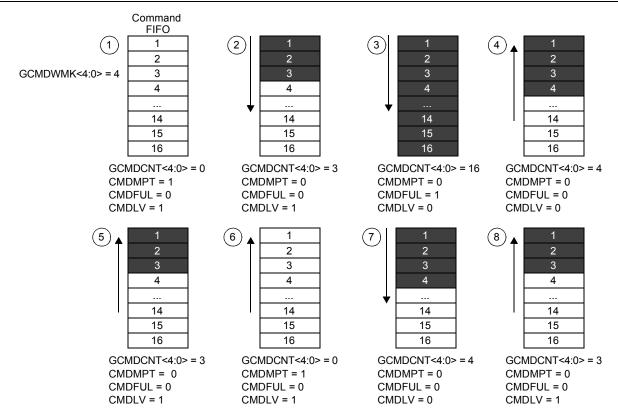

- G1CON1 Display Control Register 1 (Register 43-3) This register controls the enabling of the GFX module, sets the watermark level that triggers the interrupt for a number of queued commands in the command FIFO and sets up the color depth of the GPU operations in bits-per-pixel (bpp). This register also holds the status of the current queued commands in the 16-deep command FIFO.

- G1CON2 Display Control Register 2 (Register 43-4)

This register sets up the type of display glass hooked up to the module, the display color depth in bits-per-pixel, the display data stagger control to reduce simultaneous switching output noise and the type of test pattern that will be generated on the screen when in test mode.

- G1CON3 Display Control Register 3 (Register 43-5)

This register controls the display power signal, polarities and enabling of the display clock, vertical and horizontal synchronization, and data enable signals.

- G1STAT Status Register (Register 43-6)

This register contains the status of the GPUs, vertical/horizontal blanking, command watermark level and command FIFO.

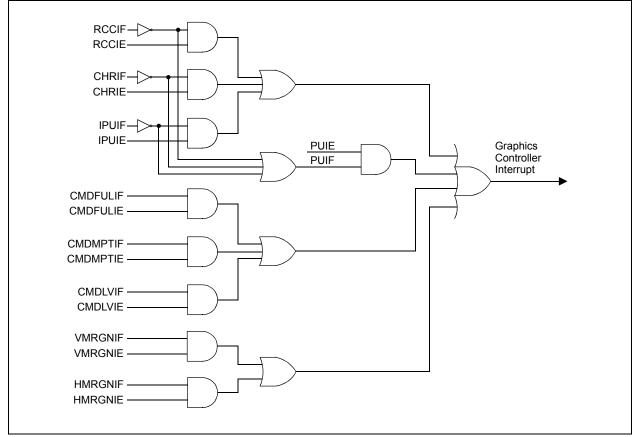

- G1IE Interrupt Enable Register (Register 43-7)

This register contains the control bits to enable the different module's interrupt sources that go to the CPU.

- G1IR Interrupt Status Register (Register 43-8) This register contains the current status of the module's interrupt sources.

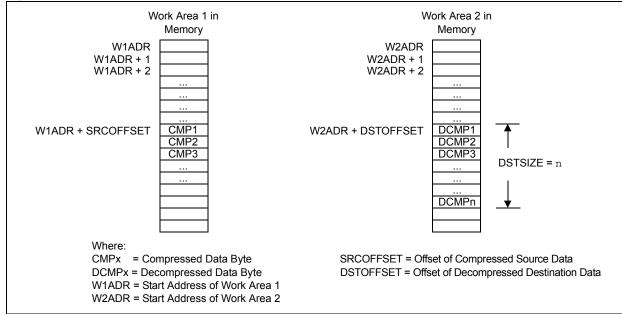

- G1W1ADRL and G1W1ADRH GPU Work Area 1 Start Address Register Low/High (Register 43-9 and Register 43-10)

These registers define Work Area 1; they specifically define the start of the memory address on which the GPU will operate. All GPUs use these two registers to define their work areas.

G1W2ADRL and G1W2ADRH – GPU Work Area 2 Start Address Register Low/High (Register 43-11 and Register 43-12)

These registers define Work Area 2; they specifically define the start of the memory address on which the GPU will operate. IPU and RCCGPU use these two registers to define its  $2^{nd}$  work area.

- G1PUW GPU Work Area Width Register (Register 43-13)

This register defines the GPU Work Areas 1 and 2 width in pixels.

- G1PUH GPU Work Area Height Register (Register 43-14)

This register defines the GPU Work Areas 1 and 2 height in pixels.

- G1DPADRL and G1DPADRH Display Buffer Start Address Register Low/High (Register 43-15 and Register 43-16)

- These registers define the start address of the display buffer.

- G1DPW Display Buffer Width Register (Register 43-17) This register defines the display buffer width in pixels.

- G1DPH Display Buffer Height Register (Register 43-18) This register defines the display buffer height in pixels.

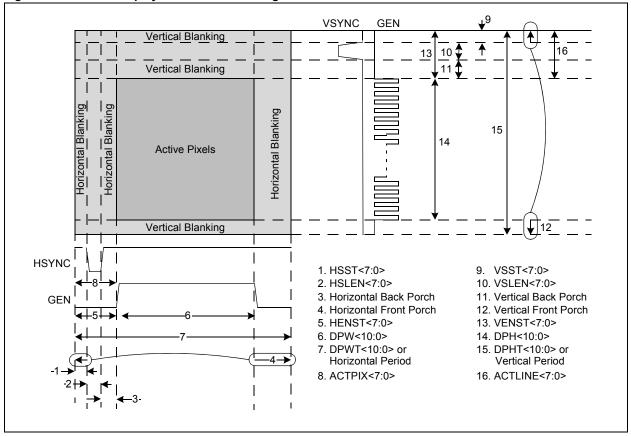

- G1DPWT Display Total Width Register (Register 43-19)

This register defines the total width of the display in pixels. This parameter may be greater than the actual pixels displayed because of the vertical, non-display blanking requirement in TFT displays.

- G1DPHT Display Total Height Register (Register 43-20)

This register defines the total height of the display in pixels. This parameter may be greater than the actual pixels displayed because of the horizontal, non-display blanking requirement in TFT displays.

- G1ACTDA Active Display Area Register (Register 43-21)

This register controls the number of lines before the first visible line is drawn and the number of display clocks before the first visible pixel is drawn.

- G1HSYNC Horizontal Synchronization Control Register (Register 43-22) This register controls the horizontal synchronization pulse width and the start of the synchronization signal.

- G1VSYNC Vertical Synchronization Control Register (Register 43-23) This register controls the vertical synchronization pulse width and the start of the synchronization signal.

- G1DBLCON Display Blanking Control Register (Register 43-24)

This register controls the number of lines between the start of the vertical blanking and the first displayed line, and the number of display clock cycles before data enable that indicates the first valid data for each line.

- G1CLUT Color Look-up Table Control Register (Register 43-25)

This register enables the CLUT usage, CLUT read/write enable bit, CLUT read trigger bit and the address of the CLUT entry that will be read or modified. This register also contains the CLUT read/write busy bit.

- G1CLUTWR CLUT Memory Write Data Register (Register 43-26) This register specifies the data written to the CLUT memory with the address specified in the G1CLUT register.

- G1CLUTRD CLUT Memory Read Data Register (Register 43-27)

This register specifies the data read from the CLUT memory with the address specified in the G1CLUT register.

- G1MRGN Interrupt Advance Register (Register 43-28)

This register specifies the number of vertical and horizontal blanking bits that will trigger in advance the interrupts for the vertical and horizontal blanking signals.

- G1CHRX and G1CHRY Character X and Y Coordinate Print Position Register (Register 43-29 and Register 43-30)

These registers specify the X and Y coordinate position of the character to be rendered in the image buffer by the CHRGPU.

- G1IPU Inflate Processor Status Register (Register 43-31)

This register contains the status bits associated with the inflate processor.

- G1DBEN Data I/O Pad Enable Register (Register 43-32)

This register controls the enabling of the I/O pads to switch to the display controller.

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|---------|--------|--------|--------|--------|--------|-------|-------|

| GCMD15  | GCMD14 | GCMD13 | GCMD12 | GCMD11 | GCMD10 | GCMD9 | GCMD8 |

| bit 15  |        |        |        |        |        |       | bit 8 |

|         |        |        |        |        |        |       |       |

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| GCMD7   | GCMD6  | GCMD5  | GCMD4  | GCMD3  | GCMD2  | GCMD1 | GCMD0 |

| bit 7   |        |        | •      |        |        |       | bit 0 |

|         |        |        |        |        |        |       |       |

| Legend: |        |        |        |        |        |       |       |

|         | 1.11   |        |        |        |        | (01   |       |

#### Register 43-1: G1CMDL: GPU Command Low Register

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 GCMD<15:0>: Low GPU Command bits

The full 32-bit command is defined by G1CMDH and G1CMDL (GCMD<31:0>). Writes to this register will not trigger the loading of GCMD<31:0> to the command FIFO. For command FIFO loading, see the G1CMDH register description.

#### Register 43-2: G1CMDH: GPU Command High Register

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| GCMD31 | GCMD30 | GCMD29 | GCMD28 | GCMD27 | GCMD26 | GCMD25 | GCMD24 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| GCMD23 | GCMD22 | GCMD21 | GCMD20 | GCMD19 | GCMD18 | GCMD17 | GCMD16 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 15-0 GCMD<31:16>: High GPU Command bits

The full 32-bit command is defined by G1CMDH and G1CMDL (GCMD<31:0>). A word write to the G1CMDH register triggers the loading of GCMD<31:0> to the command FIFO. Byte writes to G1CMDH are allowed, but only a high byte write will trigger the command loading to the FIFO. Low byte write to this register will only update the G1CMDH<7:0> bits.

| Register 43  | -3: G1CO                                                                          | N1: Display                                                                                                                               | Control Regist                                                                                                                | er 1                                                                             |                                                                               |                                                |                                                                     |

|--------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------|

| R/W-0        | U-0                                                                               | R/W-0                                                                                                                                     | R/W-0                                                                                                                         | R/W-0                                                                            | R/W-0                                                                         | R/W-0                                          | R/W-0                                                               |

| G1EN         | _                                                                                 | G1SIDL                                                                                                                                    | GCMDWMK4                                                                                                                      | GCMDWMK3                                                                         | GCMDWMK2                                                                      | GCMDWMK1                                       | GCMDWMK0                                                            |

| bit 15       |                                                                                   |                                                                                                                                           |                                                                                                                               |                                                                                  |                                                                               |                                                | bit 8                                                               |

|              |                                                                                   |                                                                                                                                           |                                                                                                                               |                                                                                  |                                                                               |                                                |                                                                     |

| R/W-0        | R/W-0                                                                             | R/W-0                                                                                                                                     | R-0                                                                                                                           | R-0                                                                              | R-0                                                                           | R-0                                            | R-0                                                                 |

| PUBPP2       | PUBPP1                                                                            | PUBPP0                                                                                                                                    | GCMDCNT4                                                                                                                      | GCMDCNT3                                                                         | GCMDCNT2                                                                      | GCMDCNT1                                       | GCMDCNT0                                                            |

| bit 7        |                                                                                   |                                                                                                                                           |                                                                                                                               |                                                                                  |                                                                               |                                                | bit 0                                                               |

|              |                                                                                   |                                                                                                                                           |                                                                                                                               |                                                                                  |                                                                               |                                                |                                                                     |

| Legend:      |                                                                                   |                                                                                                                                           |                                                                                                                               |                                                                                  |                                                                               |                                                |                                                                     |

| R = Readab   | ole bit                                                                           | W = Writabl                                                                                                                               | e bit                                                                                                                         | U = Unimpleme                                                                    | ented bit, read a                                                             | s '0'                                          |                                                                     |

| -n = Value a | It POR                                                                            | '1' = Bit is s                                                                                                                            | et                                                                                                                            | '0' = Bit is clear                                                               | ed                                                                            | x = Bit is unkno                               | own                                                                 |

| bit 15       | 1 = Display                                                                       | lule Enable b<br>module enal<br>module disa                                                                                               | bled                                                                                                                          |                                                                                  |                                                                               |                                                |                                                                     |

| bit 14       |                                                                                   | ented: Read                                                                                                                               |                                                                                                                               |                                                                                  |                                                                               |                                                |                                                                     |

| bit 13       | -                                                                                 | op in Idle bit                                                                                                                            |                                                                                                                               |                                                                                  |                                                                               |                                                |                                                                     |

|              | 1 = Display                                                                       | module stop                                                                                                                               | s in Idle mode<br>s not stop in Idle                                                                                          | e mode                                                                           |                                                                               |                                                |                                                                     |

| bit 12-8     |                                                                                   |                                                                                                                                           | Imand FIFO Wa                                                                                                                 |                                                                                  |                                                                               |                                                |                                                                     |

|              | GCMDWMk<br>10000 = If<br>01111 = If<br>00001 = If<br>int                          | <pre>&lt;&lt;4:0&gt; &gt; 100 the number of terrupt will tri the number of terrupt will tri the number the number terrupt will tri </pre> | of commands pr<br>gger and the Cl<br>of commands pr<br>gger and the Cl<br>gger and the Cl<br>of commands p<br>gger and the Cl | resent in the FIF<br>MDLV flag will be<br>resent in the FIF<br>MDLV flag will be | O goes from 16<br>e set<br>O goes from 15<br>e set<br>FO goes from 6<br>e set | to 15 command<br>to 14 command<br>to 0 command | IDLV flag.<br>ds, the CMDLVIF<br>ds, the CMDLVIF<br>ds, the CMDLVIF |

| bit 7-5      | PUBPP<2:0                                                                         | )>: GPU bits                                                                                                                              | -per-pixel Settin                                                                                                             | g bits                                                                           |                                                                               |                                                |                                                                     |

|              | Other = Res<br>100 = 16 k<br>011 = 8 bi<br>010 = 4 bi<br>001 = 2 bi<br>000 = 1 bi | oits-per-pixel<br>ts-per-pixel<br>ts-per-pixel<br>ts-per -pixel                                                                           |                                                                                                                               |                                                                                  |                                                                               |                                                |                                                                     |

| bit 4-0      | <b>GCMDCNT</b><br>When FIFO<br>10000 = 16                                         | <4:0>: Comr<br>is full, any a<br>commands                                                                                                 |                                                                                                                               |                                                                                  |                                                                               | carded.                                        |                                                                     |

|              |                                                                                   |                                                                                                                                           | esent in the FIF<br>resent in the FIF                                                                                         |                                                                                  |                                                                               |                                                |                                                                     |

### ON1: Display Control Pogistor 1

# PIC24F Family Reference Manual

| Register 43-4:  | G1CON2: Dis                                                                                                                                            | splay Control             | Register 2       |                |                   |                  |               |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|----------------|-------------------|------------------|---------------|--|--|--|--|

| R/W-0           | R/W-0                                                                                                                                                  | R/W-0                     | R/W-0            | U-0            | U-0               | R/W-0            | R/W-0         |  |  |  |  |

| DPGWDTH1        | DPGWDTH0                                                                                                                                               | DPSTGER1                  | DPSTGER0         | _              |                   | DPTEST1          | DPTEST0       |  |  |  |  |

| bit 15          |                                                                                                                                                        |                           |                  |                |                   |                  | bit 8         |  |  |  |  |

|                 |                                                                                                                                                        |                           |                  |                |                   |                  |               |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                  | R/W-0                     | U-0              | U-0            | R/W-0             | R/W-0            | R/W-0         |  |  |  |  |

| DPBPP2          | DPBPP1                                                                                                                                                 | DPBPP0                    |                  | —              | DPMODE2           | DPMODE1          | DPMODE0       |  |  |  |  |

| bit 7           |                                                                                                                                                        |                           |                  |                |                   |                  | bit (         |  |  |  |  |

| Legend:         |                                                                                                                                                        |                           |                  |                |                   |                  |               |  |  |  |  |

| R = Readable    | bit                                                                                                                                                    | W = Writable              | bit              | U = Unimo      | plemented bit, re | ead as '0'       |               |  |  |  |  |

| -n = Value at F |                                                                                                                                                        | '1' = Bit is set          |                  | '0' = Bit is   |                   | x = Bit is unkn  | own           |  |  |  |  |

| iii valdo at i  | ÖN                                                                                                                                                     | 1 Bit lo oot              |                  | o Bitio        |                   |                  |               |  |  |  |  |

| bit 15-14       | DPGWDTH<1:                                                                                                                                             | 0>: STN Displ             | ay Glass Data    | Width bits     |                   |                  |               |  |  |  |  |

|                 | 11 = Reserved                                                                                                                                          |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 10 = 16 bits wide                                                                                                                                      |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 01 = 8 bits wide                                                                                                                                       |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 00 = 4 bits wide                                                                                                                                       |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | These bits have no effect on TFT mode. The TFT display glass data width is always assumed to be 16 bits wide.                                          |                           |                  |                |                   |                  |               |  |  |  |  |

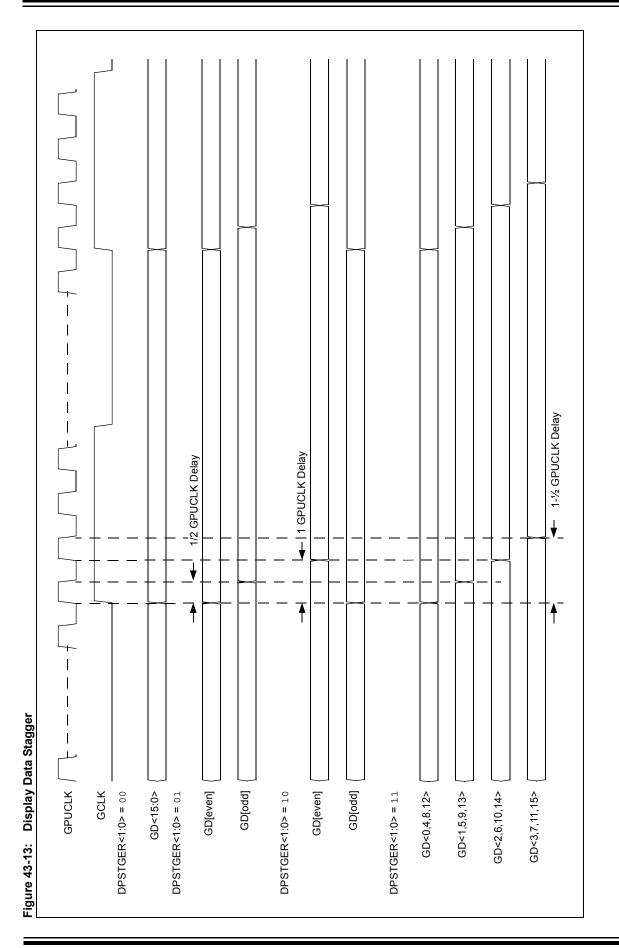

| bit 13-12       | DPSTGER<1:                                                                                                                                             | <b>0&gt;:</b> Display Dat | ta Timing Stag   | er bits        |                   |                  |               |  |  |  |  |

|                 | Refer to sectio                                                                                                                                        |                           |                  |                | ails.             |                  |               |  |  |  |  |

|                 | 11 = Delays o                                                                                                                                          | •                         |                  |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        | 0 0: 0 4 8 12 –           |                  | •              |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        |                           | delayed by 1/2 ( |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        |                           | - delayed by fu  |                |                   |                  |               |  |  |  |  |

|                 | Bit Group 3: 3 7 11 15 – delayed by 1½ GPUCLK cycle<br>10 = Even bits of the display data are delayed by 1 full GPUCLK cycle; odd bits are not delayed |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 01 = Odd bits of the display data are delayed by ½ GPUCLK cycle; even bits are not delayed                                                             |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 00 = Display o                                                                                                                                         | lata timing is a          | ll synchronized  | on one GP      | UCLK edge         |                  |               |  |  |  |  |

| bit 11-10       | Unimplemente                                                                                                                                           | ed: Read as '0            | ,                |                |                   |                  |               |  |  |  |  |

| bit 9-8         | DPTEST<1:0>: Display Test Pattern Generator bits                                                                                                       |                           |                  |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        |                           | est the interfac | e to the disp  | olay glass witho  | ut the need to a | set up memory |  |  |  |  |

|                 | interface and d                                                                                                                                        | lisplay buffer.           |                  |                |                   |                  |               |  |  |  |  |

|                 | 11 = Borders<br>10 = Bars                                                                                                                              |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 01 = Black scr                                                                                                                                         | een                       |                  |                |                   |                  |               |  |  |  |  |

|                 | 00 = Normal Display mode, test patterns are off                                                                                                        |                           |                  |                |                   |                  |               |  |  |  |  |

| bit 7-5         | DPBPP<2:0>:                                                                                                                                            | Display bits-pe           | er-pixel Setting | bits           |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        |                           | SPU bits-per-pi  | xel set in the | e PUBPP<2:0>      | (G1CON1<7:5      | >) bits.      |  |  |  |  |

|                 |                                                                                                                                                        | s-per-pixel               |                  |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        | per-pixel                 |                  |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        | -per-pixel<br>-per-pixel  |                  |                |                   |                  |               |  |  |  |  |

|                 | 000 = 2  bits<br>000 = 1  bit-p                                                                                                                        |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | Other = Reser                                                                                                                                          |                           |                  |                |                   |                  |               |  |  |  |  |

| bit 4-3         | Unimplemente                                                                                                                                           | ed: Read as '0            | 1                |                |                   |                  |               |  |  |  |  |

| bit 2-0         | DPMODE<2:0                                                                                                                                             | >: Display Glas           | ss Type bits     |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        | STN type                  | -                |                |                   |                  |               |  |  |  |  |

|                 | 010 = Mono STN type                                                                                                                                    |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 001 = TFT ty                                                                                                                                           |                           |                  |                |                   |                  |               |  |  |  |  |

|                 | 000 = Displa<br>Other = Reser                                                                                                                          | -                         |                  |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        | veu                       |                  |                |                   |                  |               |  |  |  |  |

|                 |                                                                                                                                                        |                           |                  |                |                   |                  |               |  |  |  |  |

| U-0                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                      | U-0                                                           | U-0             | U-0                                 | U-0              | R/W-0           | R/W-0   |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------|-------------------------------------|------------------|-----------------|---------|--|--|--|--|--|

| _                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                        |                                                               |                 |                                     |                  | DPPINOE         | DPPOWER |  |  |  |  |  |

| bit 15                                                                                                                                                                                                        |                                                                                                                                                                                                                                                          |                                                               | ·               |                                     |                  | •               | bit 8   |  |  |  |  |  |

| R/W-0                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                    | R/W-0                                                         | R/W-0           | R/W-0                               | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| DPCLKPOL                                                                                                                                                                                                      | DPENPOL                                                                                                                                                                                                                                                  | DPVSPOL                                                       | DPHSPOL         | DPPWROE                             | DPENOE           | DPVSOE          | DPHSOE  |  |  |  |  |  |

| bit 7                                                                                                                                                                                                         |                                                                                                                                                                                                                                                          |                                                               |                 |                                     |                  | 1               | bit C   |  |  |  |  |  |

| Legend:                                                                                                                                                                                                       |                                                                                                                                                                                                                                                          |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| R = Readab                                                                                                                                                                                                    | le bit                                                                                                                                                                                                                                                   | W = Writable                                                  | bit             | U = Unimplem                        | nented bit, read | l as '0'        |         |  |  |  |  |  |

| -n = Value a                                                                                                                                                                                                  | It POR                                                                                                                                                                                                                                                   | '1' = Bit is set                                              |                 | '0' = Bit is clea                   | ared             | x = Bit is unki | nown    |  |  |  |  |  |

| bit 15-10                                                                                                                                                                                                     | Unimplemen                                                                                                                                                                                                                                               | ted: Read as '                                                | כ'              |                                     |                  |                 |         |  |  |  |  |  |

| bit 9                                                                                                                                                                                                         | Unimplemented: Read as '0'<br>DPPINOE: Display Pin Output Pad Enable bit                                                                                                                                                                                 |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | DPPINOE is the master output enable and must be set to allow GDBEN<15:0>, DPENOE, DPPWROE DPVSOE and DPHSOE to enable the associated pads.                                                                                                               |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 1 = Enable display output pads                                                                                                                                                                                                                           |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 0 = Disable display output pads                                                                                                                                                                                                                          |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | Pins used by the signals are assigned to the next enabled module that uses the same pins. For data signals, GDBEN<15:0> can be used to disable or enable specific data signals while DPPINOE is set. <b>DPPOWER:</b> Display Power Sequencer Control bit |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

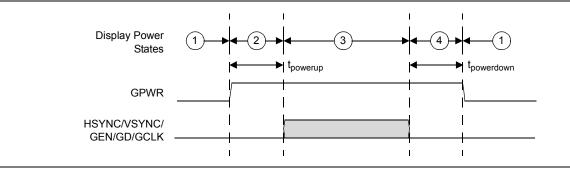

| bit 8                                                                                                                                                                                                         |                                                                                                                                                                                                                                                          |                                                               |                 | itrol bit<br><b>quencing"</b> for d | letails)         |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 1 = Set display power sequencer control port (GPWR) to '1'                                                                                                                                                                                               |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 0 = Set display power sequencer control port (GPWR) to '0'                                                                                                                                                                                               |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 7                                                                                                                                                                                                         | <b>DPCLKPOL:</b> Display Glass Clock (GCLK) Polarity bit<br>1 = Display latches data on positive edge of GCLK                                                                                                                                            |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | <ul> <li>1 = Display latches data on positive edge of GCLK</li> <li>0 = Display latches data on negative edge of GCLK</li> </ul>                                                                                                                         |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 6                                                                                                                                                                                                         | DPENPOL: Display Enable Signal (GEN) Polarity bit                                                                                                                                                                                                        |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | For TFT mode (DPMODE (G1CON2<2:0>) = $001$ ):                                                                                                                                                                                                            |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 1 = Active-high (GEN)<br>0 = Active-low (GEN)                                                                                                                                                                                                            |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | For STN mode (DPMODE (G1CON2<2:0>) = 010 or 011):                                                                                                                                                                                                        |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 1 = GEN connects to shift clock input of the display (Shift Clock mode)                                                                                                                                                                                  |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 5                                                                                                                                                                                                         | <ul> <li>0 = GEN connects to MOD input of the display (Line/Frame Toggle mode)</li> <li>DPVSPOL: Display Vertical Synchronization (VSYNC) Polarity bit</li> </ul>                                                                                        |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 5                                                                                                                                                                                                         | 1 = Active-hig                                                                                                                                                                                                                                           |                                                               | Gynchionizatio  |                                     | anty bit         |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 0 = Active-lov                                                                                                                                                                                                                                           |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 4                                                                                                                                                                                                         | DPHSPOL: Display Horizontal Synchronization (HSYNC) Polarity bit                                                                                                                                                                                         |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | 1 = Active-hig<br>0 = Active-lov                                                                                                                                                                                                                         |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 3                                                                                                                                                                                                         |                                                                                                                                                                                                                                                          | . ,                                                           | Seauencer Co    | ntrol Port (GPW                     | /R) Enable bit   |                 |         |  |  |  |  |  |

| bit 3 <b>DPPWROE:</b> Display Power Sequencer Control Port (GPWR) Enable bit<br>1 = GPWR port enabled (pin controlled by DPPOWER (G1CON3<8>) bit)<br>0 = GPWR port disabled (pin can be used as ordinary I/O) |                                                                                                                                                                                                                                                          |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| bit 2                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                        | splay Enable P                                                |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                        | = GEN port enabled                                            |                 |                                     |                  |                 |         |  |  |  |  |  |

|                                                                                                                                                                                                               | <ul> <li>0 = GEN port disabled</li> <li>DPVSOE: Display Vertical Synchronization Port Enable bit</li> </ul>                                                                                                                                              |                                                               |                 |                                     |                  |                 |         |  |  |  |  |  |

| hit 1                                                                                                                                                                                                         |                                                                                                                                                                                                                                                          | disabled                                                      | un obranication | Dort Enable 11                      |                  |                 |         |  |  |  |  |  |

| bit 1                                                                                                                                                                                                         | DPVSOE: Dis                                                                                                                                                                                                                                              | disabled<br>splay Vertical S                                  | ynchronization  | Port Enable bit                     | t                |                 |         |  |  |  |  |  |

| bit 1                                                                                                                                                                                                         |                                                                                                                                                                                                                                                          | disabled<br>splay Vertical S<br>oort enabled                  | ynchronization  | Port Enable bit                     | t                |                 |         |  |  |  |  |  |

| bit 1<br>bit 0                                                                                                                                                                                                | <b>DPVSOE:</b> Dis<br>1 = VSYNC p<br>0 = VSYNC p                                                                                                                                                                                                         | disabled<br>splay Vertical S<br>port enabled<br>port disabled | -               | I Port Enable bit                   |                  |                 |         |  |  |  |  |  |

| R-0               | U-0                                                                                                                                                         | U-0                        | U-0             | U-0                | U-0              | U-0             | U-0         |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|--------------------|------------------|-----------------|-------------|--|--|--|--|--|

| PUBUSY            | _                                                                                                                                                           |                            |                 | _                  | _                | _               | _           |  |  |  |  |  |

| bit 15            |                                                                                                                                                             | •                          |                 |                    |                  |                 | bit 8       |  |  |  |  |  |

|                   |                                                                                                                                                             |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| R-0               | R-0                                                                                                                                                         | R-0                        | R-0             | R-0                | R-0              | R-0             | R-0         |  |  |  |  |  |

| IPUBUSY           | RCCBUSY                                                                                                                                                     | CHRBUSY                    | VMRGN           | HMRGN              | CMDLV            | CMDFUL          | CMDMPT      |  |  |  |  |  |

| bit 7             |                                                                                                                                                             |                            |                 |                    |                  |                 | bit         |  |  |  |  |  |

| Legend:           |                                                                                                                                                             |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| R = Readab        | le bit                                                                                                                                                      | W = Writable b             | it              | U = Unimpleme      | nted bit. read a | s '0'           |             |  |  |  |  |  |

| -n = Value at POR |                                                                                                                                                             | '1' = Bit is set           |                 | '0' = Bit is clear |                  | x = Bit is unkn | own         |  |  |  |  |  |

|                   |                                                                                                                                                             |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 15            | PUBUSY: P                                                                                                                                                   | rocessing Units            | are Busy State  | us bit             |                  |                 |             |  |  |  |  |  |

|                   | This bit is logically equivalent to the ORed combination of IPUBUSY, RCCBUSY and CHRBUSY.                                                                   |                            |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | <ul> <li>1 = At least one processing unit is busy</li> <li>0 = None of the processing units is busy</li> </ul>                                              |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 14-8          |                                                                                                                                                             |                            | -               |                    |                  |                 |             |  |  |  |  |  |

| bit 7             | Unimplemented: Read as '0'<br>IPUBUSY: Inflate Processing Unit Busy Status bit                                                                              |                            |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | 1 = IPU is b                                                                                                                                                |                            | g offit Duby of |                    |                  |                 |             |  |  |  |  |  |

|                   | 0 = IPU is n                                                                                                                                                |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 6             | RCCBUSY: Rectangle Copy Graphics Processing Unit Busy Status bit                                                                                            |                            |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | 1 = RCCGP<br>0 = RCCGP                                                                                                                                      | U is busy<br>U is not busy |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 5             | CHRBUSY: Character Graphics Processing Unit Busy Status bit                                                                                                 |                            |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | 1 = CHRGPU is busy                                                                                                                                          |                            |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | 0 = CHRGPU is not busy                                                                                                                                      |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 4             |                                                                                                                                                             | ertical Blanking S         |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | <ul> <li>1 = Display interface is in the vertical blanking period</li> <li>0 = Display interface is not in the vertical blanking period</li> </ul>          |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 3             | HMRGN: Horizontal Blanking Status bit                                                                                                                       |                            |                 |                    |                  |                 |             |  |  |  |  |  |

|                   |                                                                                                                                                             | interface is in th         |                 |                    |                  |                 |             |  |  |  |  |  |

|                   | 0 = Display interface is not in the horizontal blanking period                                                                                              |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 2             |                                                                                                                                                             | mmand Waterm               |                 |                    |                  |                 |             |  |  |  |  |  |

|                   |                                                                                                                                                             |                            |                 | FIFO changed from  |                  |                 |             |  |  |  |  |  |

|                   |                                                                                                                                                             |                            |                 | lue set in the GC  |                  | DN1<12:8>) regi | ister dits. |  |  |  |  |  |

|                   | <ul> <li>1 = Command in FIFO is less than the set GCMDWMK value</li> <li>0 = Command in FIFO is equal to, or greater than, the set GCMDWMK value</li> </ul> |                            |                 |                    |                  |                 |             |  |  |  |  |  |

| bit 1             |                                                                                                                                                             | command FIFO               | -               | ,                  |                  |                 |             |  |  |  |  |  |

|                   |                                                                                                                                                             | nd FIFO is full            |                 |                    |                  |                 |             |  |  |  |  |  |

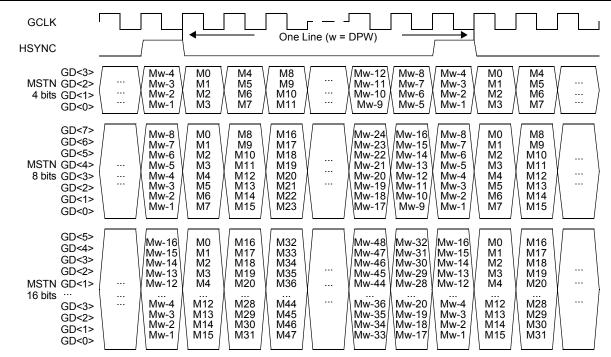

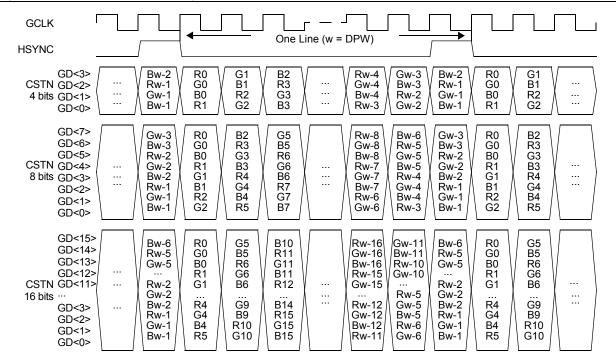

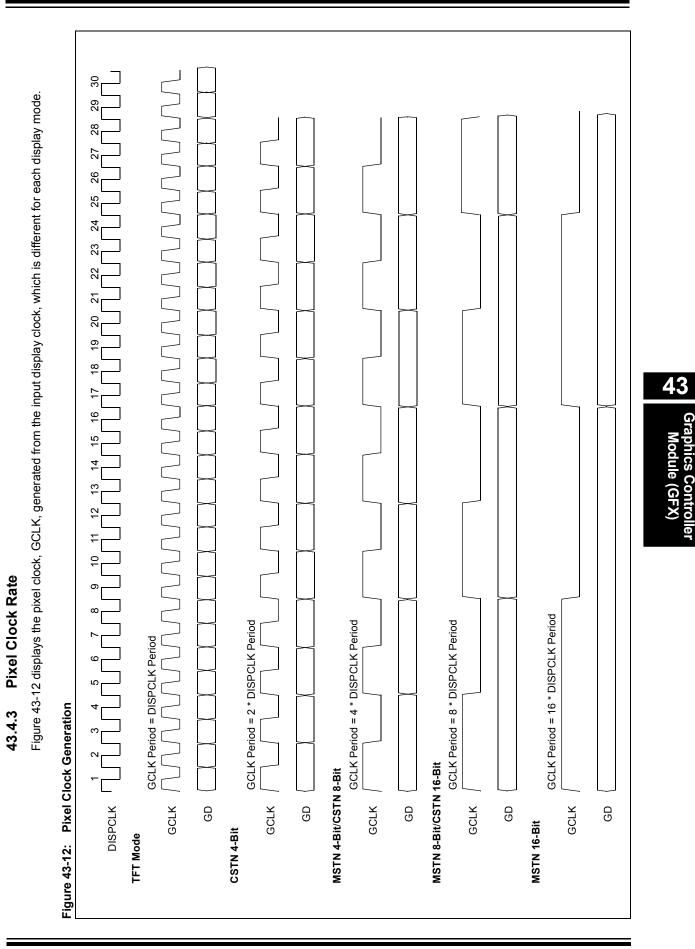

|                   | 0 = Comma                                                                                                                                                   | nd FIFO is not fu          | ll              |                    |                  |                 |             |  |  |  |  |  |